#Xilinx ISE

Text

youtube

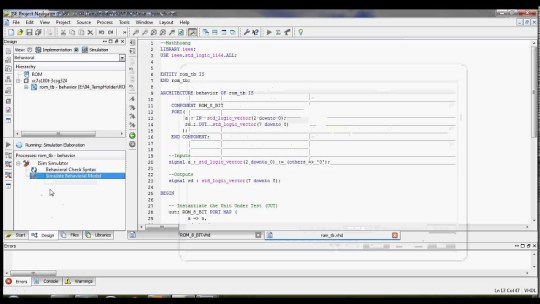

VHDL Tutorial : Your First VHDL Design: VHDL Entity & Architecture - A Beginner's Guide

Welcome to the ultimate beginner's guide for Your First VHDL Design! In this video, we will dive into the fundamentals of VHDL Entity and Architecture and provide you with a comprehensive understanding of the topic. Whether you are new to VHDL or looking to refresh your knowledge, this guide is designed to help you get started and pave your way to becoming an expert VHDL designer. In this tutorial, we will cover the basics of VHDL, starting with the VHDL Entity and its crucial role in the design process. You will learn how to define and describe the inputs and outputs of your VHDL design using the Entity section, providing the necessary specifications for your project. Moving on, we will explore the VHDL Architecture, which defines the actual implementation of your design. Through a step-by-step walkthrough, you will discover how to construct the architecture block by block, ensuring a well-structured and functional VHDL design. To make the learning experience more practical, we will dive into real-world examples and demonstrate each concept using a popular VHDL software tool. You'll witness the transition from theory to practice, gaining hands-on experience in VHDL design. With this beginner's guide, you'll not only grasp the essentials of VHDL Entity and Architecture but also acquire the ability to kickstart your own VHDL designs, opening up a wide range of possibilities in digital circuit design. Subscribe to our channel for more exciting VHDL tutorials and stay tuned for upcoming videos in this series where we will explore advanced VHDL concepts and applications.

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

#VHDL#VHDL Entity#VHDL Architecture#VHDL Design#Beginner's Guide#Digital Circuit Design#VHDL Tutorial#VHDL Basics#VHDL Examples#VHDL Software#Learn VHDL#VHDL Learning#VHDL Step-by-step#VHDL Introduction#VHDL Fundamentals#VHDL Engineering#Hardware Design#Circuit Design#Xilinx ISE#Xilinx Vivado#Digital#ASIC#Engineering#Students#Training#Tutorial#Altera#Hardware description language#modeling style#data flow

1 note

·

View note

Text

Xilinx ise 14.7 windows 10 pn.exe error

It strongly supports code reusability and code sharing.Ī list of disadvantages of VHDL is given below:.

It provides tight coupling to lower levels of design.

It provides a flexible design language.

It supports various design methodologies like Top-down approach and Bottom-up approach.

For early performance estimation of system architectureĪ list of advantages of VHDL is given below:.

2008: IEEE Standard 1076-2008 (New features) was released.

1999: Analog Mixed Signal extension (VHDL-AMS).

1996: A VHDL package used with synthesis tools and became a part of the IEEE 1076 standard.

1993: VHDL was re-standardized to enhance the language.

1987: DOD permitted for commercial purpose, and VHDL became IEEE Standard 1076-1987.

1985 (VHDL Version 7.2): The final version of the language under the government contract was released.

1983: The development of VHDL began with a joint effort by IBM, Inter-metrics, and Texas Instruments.

1980: The Department of Defence wanted to make circuit design self-documenting.

VHDL was developed by the Department of Defence (DOD) in 1980. It does not support the Multi-Dimensional array. It does not allow the user to define data types. The most popular examples of Verilog are network switch, a microprocessor, a memory, a simple flip-flop, etc. It is used in both hardware simulation and synthesis. Verilog is also a HDL (Hardware Description Languages) for describing electronic circuits and systems.

Design methodologies and their features.

The most popular examples of VHDL are Odd Parity Generator, Pulse Generator, Priority Encoder, Behavioral Model for 16 words, 8bit RAM, etc. It is an IEEE (Institute of Electrical and Electronics Engineers) standard hardware description language that is used to describe and simulate the behavior of complex digital circuits.

VHDL stands for Very High-Speed Integration Circuit HDL (Hardware Description Language). Today, there are many HDLs available in the market, but VHDL and Verilog are the most popular HDLs.

The main advantage of HDLs is that it provides flexible modeling capabilities and can express the large complex designs (>10 7 gates). HDL is mainly used to discover the faults in the design before implementing it in the hardware. It is a programming language that is used to describe, simulate, and create hardware like digital circuits (ICS). HDL stands for Hardware Description Language.

Creating a Project in VHDL using the Xilinx IDE tool.

Our VHDL tutorial is designed for beginners and professionals. VHDL tutorial provides basic and advanced concepts of VHDL.

0 notes

Text

تقنيات جامعية: تصميم دائرة فلب فلوب(S-R Flip Flop) باستخدام لغة الvhdl على برنامج xilinx ise 9.2i

youtube

تهدف لغة VHDL (VHSIC Hardware Description Language) إلى تصميم الأنظمة الإلكترونية الرقمية. تعتبر VHDL من أشهر اللغات المستخدمة في تصميم الأنظمة الرقمية، وتستخدم بشكل واسع في صناعة الدوائر المتكاملة والمنتجات الإلكترونية الأخرى. تم تطوير VHDL في الأصل بواسطة وزارة الدفاع الأمريكية في الثمانينيات، كجزء من مشروع VHSIC (Very High-Speed Integrated Circuit) الذي كان يهدف إلى تطوير تقنيات التصنيع الدقيقة للدوائر المتكاملة. وقد تم نشر نسخة من اللغة للاستخدام العام في عام 1987. تتميز VHDL بقدرتها على وصف التصميم الإلكتروني بشكل دقيق ومفصل، مما يسمح للمصممين بإنشاء نماذج للأنظمة الرقمية واختبارها قبل تصنيعها. تساعد VHDL على تحديد الوظائف التي يجب أن تقوم بها الأجزاء المختلفة من النظام وكيفية تفاعلها مع بعضها البعض. تتكون لغة VHDL من عدة عناصر، بما في ذلك المكونات (components) والعمليات (processes) والإجراءات (procedures) والدوال (functions) والنماذج (models). تستخدم VHDL لوصف الأنظمة الرقمية بشكل هيكلي، مما يسهل فهم تصميم النظام وتحليله. على الرغم من أن VHDL قد تم تصميمها بشكل أساسي لتصميم الأنظمة الرقمية، إلا أنها يمكن استخدامها أيضًا في تصميم الأنظمة الأخرى مثل النظم الميكانيكية والكهروميكانيكية. بشكل عام، تتيح لغة VHDL للمصممين إنشاء نماذج للأنظمة الرقمية وتحليلها وتصحيح الأخطاء قبل تصنيعها، مما يوفر الكثير من الوقت والجهد والتكلفة في عملية التصميم والإنتاج. وتعد VHDL أيضًا مفيدة في توثيق التصميم وتقييمه، حيث يمكن استخدام الشفرة المصدرية لتوثيق تفاصيل التصميم وتحليل الأداء. يتم تنفيذ الأنظمة الرقمية المصممة باستخدام VHDL عن طريق ترجمة الشفرة المصدرية إلى ملفات التصميم القابلة للتصنيع. ويمكن استخدام برامج مختلفة لتحليل وتصحيح التصميم المصمم باستخدام VHDL، مثل Xilinx ISE و ModelSim و Quartus. بشكل عام، تعد VHDL أداة قوية وفعالة في تصميم الأنظمة الرقمية، وهي مفيدة في العديد من الصناعات التقنية. وتحظى بشعبية كبيرة في صناعة الدوائر المتكاملة والإلكترونيات الرقمية والاتصالات والعديد من التطبيقات الأخرى. #xilinx# #ise #9.2i#

0 notes

Text

16 bit bcd adder vhdl tutorial pdf

16 BIT BCD ADDER VHDL TUTORIAL PDF >>Download

vk.cc/c7jKeU

16 BIT BCD ADDER VHDL TUTORIAL PDF >> Read Online

bit.do/fSmfG

This VHDL manual is based on the older IEEE Standard 1076-1987. The cation,thewidth of the result is 16 bit, which is equal to the sum of the. The VHDL Cookbook - First Edition (by Peter J. Ashenden) (pdf); Dispensa di VHDL (pdf) Esercitazione 5: costruzione e test di un full adder a 8 bit Roberto Giorgi, Universita' di Siena, C116L01, Slide 16 Full Adder a 1 bit Da: Intel® 64 and IA-32 Architectures Software Developer's Manual, Giovanni De · PDF fileoperazioni di addizione fra bit. (VHDL code) Full Adder con porte. VHDL tutorial using Aldec VHDL software. I linguaggi HDL attualmente più utilizzati sono il VHDL (VHSIC, Very High Speed Integrated Circuits HDL) e il. Verilog. I concetti alla base dei due Tutorial rivolto agli studenti per l'utilizzo del software Xilinx-ISE Free WEBPACK Creazione di un file VHDL · Creazione di una Macchina a Stati FinitiTurn your PDF publications into a flip-book with our unique Google with BCD select DOUT : out std_logic_vector(15 downto 0); — Uscita (16 bit). Guida all'utilizzo di VHDL a cura del professor Stefano Mattoccio by francesco_platoni. Adder a 4 bit, si presta ad essere facilmente esteso al caso

https://www.tumblr.com/baqohudene/697779744444383232/sleep-hygiene-pdf-nhs, https://www.tumblr.com/baqohudene/697779584647790592/olympus-vr-340-manual, https://www.tumblr.com/baqohudene/697779584647790592/olympus-vr-340-manual, https://www.tumblr.com/baqohudene/697779461558534144/faerie-winter-janni-lee-simner-pdf-editor, https://www.tumblr.com/baqohudene/697780024978325504/enfermedades-de-los-ojos-pdf-editor.

0 notes

Text

CSc ) Project 05 Solution

CSc ) Project 05 Solution

IMPORTANT!

Please follow the submission guidelines below or your submission will be rejected.

You are expected to submit both a lab report and the source files to Blackboard in a single submission attempt.

The source codes must be under a single project.

The VHDL project needs to be exported from Xilinx ISE Design Suite. To export VHDL project file, please refer to Blackboard -> Content -> Lab…

View On WordPress

0 notes

Text

PROJECT 1Getting to know Verilog and Xilinx ISE Solution

PROJECT 1Getting to know Verilog and Xilinx ISE Solution

Introduction

In this lab, you will learn the basics of Verilog as a hardware description language, and get more familiar with the Xilinx ISE as your simulation and synthesis tool. You need to provide the simulation, validate the design, and explain the procedure to implement it on an actual board as you were taught (since the course is online, the mere explanation is enough). You need to provide…

View On WordPress

0 notes

Photo

Yosys Fronts for Xilinx ISE #fpga #verilog #xilinx #yosys https://t.co/Kpejbx9Vzy http://twitter.com/iAndroideu/status/1205903395216752640

Yosys Fronts for Xilinx ISE #fpga #verilog #xilinx #yosys https://t.co/Kpejbx9Vzy

— iAndroid.eu (@iAndroideu) December 14, 2019

0 notes

Text

youtube

Where to Download Xilinx ISE v14.7 for Windows 10 or Windows 11 for free

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/archive-ise.html Once you open it, click on Last updated ISE design suite for windows 10, here it is version 14.7 Windows 10, last update of Feb-2020. Setup file is 15GB in file size, so click on the setup file and wait for the download to complete. The download is Zipped, so once the file is downloaded completely, Unzip the folder and follow the installation instruction. If you are getting any error while installation, Please go through the links in description to get the steps fixing those. Xilinx ISE v14.7 Installation Error on Windows 10 or Windows 11 - Solved! https://www.youtube.com/watch?v=Nfhu38Lxhw0 Virtualization Not Enabled in BIOS? Here's How to Fix It https://www.youtube.com/watch?v=vZFxIaYpuD4 Virtualization in BIOS : Enabled or Disabled? How to Check in Windows 10 / Windows 11 https://www.youtube.com/watch?v=39i6HWqjsN0

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

#Xilinx ISE#Download#Get Xilinx ISE#Install Xilinx ISE#VHDL basics#VHDL programming#VHDL tutorial#VHDL sequential statements#VHDL concurrent statements#VHDL beginner's guide#VHDL insights#VHDL concepts#VHDL design#digital design#beginner's tutorial#coding tutorial#VHDL for beginners#VHDL learning#VHDL syntax#VHDL examples#VHDL video tutorial#VHDL step-by-step#VHDL Examples#VHDL Coding#VHDL Course#VHDL#FPGA#Altera#Xilinx Vivado#VHDL Simulation

1 note

·

View note

Text

Nation Innovation

Nation Innovation aims with the vision of achieving technical upliftment and academic strengthening of skills of the youth with aid to the students irrespective of educational qualification right from the school students to the undergraduate and higher.

We visualize with providing the appropriate content, guidance and online support in order to aid in the best possible direction.

🔌Our services are:-

➡️Workshops and Hands On training in electronics softwares for practical skills upliftment.

➡️Online Tutorials on our official youtube channel.

➡️Training Programs for the undergraduate and postgraduate courses.

➡️Electronics Projects for school, undergraduate and postgraduate projects such as Xilinx ISE, Cadence Virtuoso, MATLAB, Machine Learning, Python, IoT based systems, Robotics projects, Automation Projects, Raspberry Pi, Arduino Projects, Microcontroller Projects, Image Processing, Embedded systems, Hardware implementation with PCB designed systems.

➡️Queries & Discussion

We hearty welcome all for discussions and queries including career counselling, suggestions, opportunities and prospects in the electronics domain.

#science#technology#electronics#engineering#engineers#diy projects#robotics projects#science project#tutorial#diy#diy project#diy tutorial#artificial intelligence#python#machine learning#iot application development#science and technology

1 note

·

View note

Text

Software Upgrade Tanberg V2 Tanaka T21 Samurai

Software terbaru raceiver tanaka samurai t21 v2 Software terbaru raceiver tanaka samurai t21 v2 Receiver Murah Download Software terbaru raceiver tanaka samurai t21 v2. Untuk software receiver SD (tidak semua yang SD), singkatnya memang butuh software untuk upgrade namun tak menjamin 100% akan berhasil dan berjalan baik. Tanaka T21 Segera saja pasang parabola jaring dengan receiver Tanaka t 21 new samurai murah nikmati banyak tayangan hiburan sofware bisa di upgrade (data,kernel and file TUTORIAL UPGRADE+BACKUP SOFTWARE RECEIVER TANAKA T21 MULTI Receiver TANAKA T21 Tanaka T21 New Samurai HD sw software v2 terbaru Cara Tanberg dan juga Tanaka T21.

Software Upgrade Tandberg V2 Tanaka T21 Samurai Driver

Software Upgrade Tandberg V2 Tanaka T21 Samurai Turbo

Software Upgrade Tandberg V2 Tanaka T21 Samurai X

Software Upgrade Tandberg V2 Tanaka T21 Samurai 2

Software Upgrade Tandberg V2 Tanaka T21 Samurai Parts

Kost22mbs2 rt5370openkey pbosport24 (20171015) link: jurassicsamurai. Salam min saya mau apdute resiver tanaka t22 jurassic metal sw terbarunya yang mana. SW Software Update Tanaka T22 & T21 New Samurai KOS Terbaru 2018 Download. Wii Games Iso Highly Compressed. Spoiled tool shop staff walkthrough. Tanaka T-22 jurassic, tanaka sakura, dsb). File software di download dari. File Dump Sw Tanaka T22 Jurassic World; Adapun secara fisik receiver tanaka t22 hd jurassic metal tak beda jauh dengan generasi sebelumnya tanaka jurassic hd, perbedaan yang mendasar terletak pada casing bagian atas receiver dimana generasi sebelumnya semua body berbahan plastik, untuk jurassic metal body casing bagian atas terbuat dari bahan logam. Ini bisa jadi pilihan untuk menggantikan.

Software Upgrade Tandberg V2 Tanaka T21 Samurai Driver

683.This Cognac Sour cocktail is not for the faint of heart. Can you mix cognac and whiskey.

sitlopla.netlify.com › ▲▲ Sw Tanaka T22 Hd Samurai Terbaru Lagu ▲▲

Cara upgrade sw software v2 terbaru untuk tanaka t22 hd (Software. Edit radio logo matrix s2. Tanaka T21 New Samurai HD. Download tanberg v2 tanaka 21 Software.

Software Upgrade Tandberg V2 Tanaka T21 Samurai Turbo

Roark shoots himself into his analysis rather than confronting the media. The back half of this episode is dedicated entirely to tidying up. Assessing Alex Parrish - or perhaps leaving her success a matter before later - could have been a powerful psychological cliffhanger. But rather, she instantly wakes in an ambulance, wrap up this bloody battle into yet another tidy and neat bow. Quantico season 1 download utorrent for pc.

Software Upgrade Tandberg V2 Tanaka T21 Samurai X

Sw Pbo Tanaka T22 Jurassic Pack

SoFly Welcome To SoFly!!! Please Register To Have Acces To Evrithing!!!!FORUMUL ESTE IN PLINA DEZVOLTARE VA RUGAM SA NE AJUTATI! EXTRA TAGS: Britney Spears WWE Barack Obama Miley Cyrus RuneScape Jessica Alba Naruto Lindsay Lohan Angelina Jolie American Idol Dictionary MySpace Google YouTube Facebook Coupons Cars Craigslist Online degrees Credit score nintendo wii wii fit ipod touch xbox 360 nintendo ds ipod nano uggs nikon d90 zune digital picture frame Nu sunteti logat. Nou pe simpatie.ro: cauta Barbat 21 - 36 ani / / Google Rank. Download toefl structure 2016 trucks. Curtis Advocate Din: Cotesti - Gettou Inregistrat: Postari: 955 Xara3D 5.02 X-HDL_v3.2.55 Xilinx ChipScope Pro v8.2.03i Xilinx Chipscope Pro v8.2i Xilinx EDK 8.1 (1 dvd) Xilinx EDK v8.2 XILINX Embedded Development Kit and.XPS Ver7.1 XILINX Embedded Development Kit and.XPS Ver7.1 Incl Sp2 Xilinx ISE 9.1 XILINX ISE V6.3I PROPER Xilinx ISE v7.1i Xilinx ISE v7.1i Xilinx ISE v7.1i Xilinx ISE v7.1i ISO 3CD Xilinx ISE v8.2i Xilinx ISE v9.1 Xilinx PlanAhead v8.2.2. Curtis Advocate Din: Cotesti - Gettou Inregistrat: Postari: 955 Emergency 4, Altova SchemaAgent v2007, Jenaveve Jolie- Little Miss Innocence, Grizzly Park (2008), Futurama: Bender 's Big Score!

Software Upgrade Tandberg V2 Tanaka T21 Samurai 2

Sw Pbo Tanaka T22 Jurassic Park 3

Software Upgrade Tandberg V2 Tanaka T21 Samurai Parts

Hallo semua hari ini saya ingin membahas sedikit tentang receiver yang banyak dibahas dan diburu karena kandidat pengganti dai TANAKA T22 Jurassic yang sudah discountinu, adik dari Tanaka T22 Jurassic yaitu Tanaka T21 New Samurai, selain itu juga sudah mulai ada kembarannya yaitu Tanaka New Sakura, sepertinya Receiver dengan merk tanaka suka sekali merilis RX baru yang mirip Tanaka New Samurai banyak dicari karena fiturnya mirip sekali dengan T22 Jurassicsampai ada yang bilang saudara kembaran dari T22 Jurassic.

0 notes

Text

Intel® Fpga Development Instruments Design

Our placement staff schedule placement drives and likewise conducts interview in several MNCs. Already, we've kept a average CMOS & FPGA Design Flow course charge to help college students coming from all sections of the society. Further, college students discover the CMOS & FPGA Design Flow coaching course duration flexible. CMOS & FPGA Design Flow course time is scheduled based on the coed's necessities.

The interconnect of an FPGA could be very totally different than that of a CPLD, but is somewhat just like that of a gate array ASIC. In Figure eleven, a hierarchy of interconnect sources can be seen. There are long traces which can be used to connect important CLBs which would possibly be bodily removed from each other on the chip with out inducing much delay. There are also brief traces that are used to connect individual CLBs that are positioned bodily close to each other.

They include just one performance in them and thru the lifetime of the chip, it could perform solely that perform. Its logic operate can't be changed to anything else as a result of its digital circuitry is made up of permanently connected gates and flip-flops on silicon. The difference in case of ASIC is that the resultant circuit is completely drawn into silicon whereas in FPGA the circuit is made by connecting numerous configurable blocks.

He has proficiency in SPICE, VHDL, Verilog, SystemVerilog, Xilinx ISE, Vivado, CoventorWare, COMSOL and LabVIEW programming. It may be “field” programmed to work as per the supposed design. It means it could work as a microprocessor or graphics card, and even as both directly. The designs running on FPGA’s are typically created utilizing hardware description languages such as VHDL and Verilog.

This two-day workshop in the space of FPGA design using Xilinx Vivado aims to enhance the intellectuals in direction of the design of digital circuits for real-time functions. Figure 8 FPGA Architecture Each FPGA vendor has its own FPGA architecture, but normally phrases they're all a variation of that proven in Figure 8. The structure consists of configurable logic blocks, configurable I/O blocks, and programmable interconnect. Also, there shall be clock circuitry for driving the clock signals to every logic block, and extra logic resources similar to ALUs, reminiscence, and decoders could additionally be obtainable. The two fundamental types of programmable components for an FPGA are Static RAM and anti-fuses. It is a tool that's created for a specific function or functionality.

There is commonly one or a quantity of switch matrices, like that in a CPLD, to attach these lengthy and brief strains collectively in particular ways. Programmable switches contained in the chip allow the connection of CLBs to interconnect lines and interconnect lines to each other and to the swap matrix. Three-state buffers are used to attach many CLBs to an extended line, creating a bus. Special lengthy lines, referred to as world clock traces, are specifically designed for low impedance and thus fast propagation times.

Our Electronic Design Automation ecosystem ensures that you've a whole design answer in designing, verifying, and integrating Intel® FPGAs into your methods. Find videos on the method to get began with Intel® Quartus® Prime and how to get the most effective performance on your Stratix 10 designs. This course trains you on the superior Design and Verification applied sciences and methodologies. One can simply enter into the VLSI trade with the talent units which may be gained by way of this coaching course. When the chips are put into production, it is essential to have some sort of burn-in check of your system that frequently tests your system over some lengthy period of time.

This information will allow us to route your request to the appropriate person. ITZIP conducts Personality Development periods together with Spoken English, Group Discussions, Mock Interviews, Presentation abilities to organize students Logic Fruit to face difficult interview situation with ease. ITZIP is the chief in providing placement to the students, as it has a devoted placement wing which caters to the wants of the students throughout placements.

This functionality supplies a simple methodology to confirm hardware implementation and accelerate simulations. No price training sessions are carried out on personality growth, spoken English, group dialogue, and mock interview to sharpen the presentation expertise. APTRON Gurgaon CMOS & FPGA Design Flow is all about sensible and follow; our classes embody concept and practical exposure for the students in studying. Join one of the best CMOS & FPGA Design Flow coaching in gurgaon supplied by APTRON Gurgaon to avail fast CMOS & FPGA Design Flow teaching, average course fee, and placement after Ab initio course.

The coaching happened remotely, nonetheless I really did not get the feel of distance hole. The trainer helped me to associated the course ideas with the IT industry that honed my artistic considering expertise. Attending CEH training at Multisoft Systems fulfills my objective utterly. Training starting from the basics of networking to the superior level of hacking expertise provides me nice publicity to the ethical hacking domain. Now, I’m confident sufficient to satisfy the security talent crisis of my group. The coaching was excellent and educated, filled with illustrations.

1 note

·

View note

Text

CSc) Project 04 Solution

CSc) Project 04 Solution

IMPORTANT!

Please follow the submission guidelines below or your submission will be rejected.

You are expected to submit both a lab report and the source files to Blackboard in a single submission attempt.

The source codes must be under a single project.

The VHDL project needs to be exported from Xilinx ISE Design Suite. To export VHDL project file, please refer to Blackboard -> Content -> Lab…

View On WordPress

0 notes

Text

CS M A Project 3 Solution

CS M A Project 3 Solution

Clock Design Methodology

In this lab, you will learn how to use the Xilinx ISE program to design and test various clock waveforms

Introduction

For this lab, you will use the Xilinx ISE software to design and test various clock waveforms on a digital system. The Lab will go through the basic concept behind clocking a system and the techniques to generate them from a system clock,

This lab will be…

View On WordPress

0 notes